The designs of the master and slave CCB FPGAs [Document number: A48001N004, revision 10]

Martin Shepherd, California Institute of Technology

June 8, 2005

This page intentionally left blank.

### Abstract

The aim of this document is to detail the design of the firmware in the CCB slave and master FPGAs, and define their interfaces to the rest of the CCB hardware and software. The design is presented in a hierarchical manner, starting with block diagrams of major components and their interconnections, and ending with either low level schematics, or with VHDL components.

## Contents

| 1        | Intr | oducti | ion                                     | 7  |

|----------|------|--------|-----------------------------------------|----|

| <b>2</b> | The  | slave  | $\mathbf{FPGAs}$                        | 9  |

|          | 2.1  | An ov  | erview of the internals of a slave FPGA | 9  |

|          |      | 2.1.1  | The Heartbeat Generator                 | 12 |

|          |      | 2.1.2  | The Signal Injector                     | 13 |

|          |      | 2.1.3  | The Sampler component                   | 14 |

|          |      | 2.1.4  | The Blanker component                   | 15 |

|          |      | 2.1.5  | The Integrator component                | 16 |

|          |      | 2.1.6  | The Accumulator component               | 16 |

| 3        | The  | maste  | er FPGA                                 | 21 |

|          | 3.1  | The C  | Control Gateway                         | 23 |

|          |      | 3.1.1  | The internals of the Control Gateway    | 24 |

|          | 3.2  | The D  | Oata Dispatcher                         | 40 |

|          |      | 3.2.1  | The internals of the Data Dispatcher    | 42 |

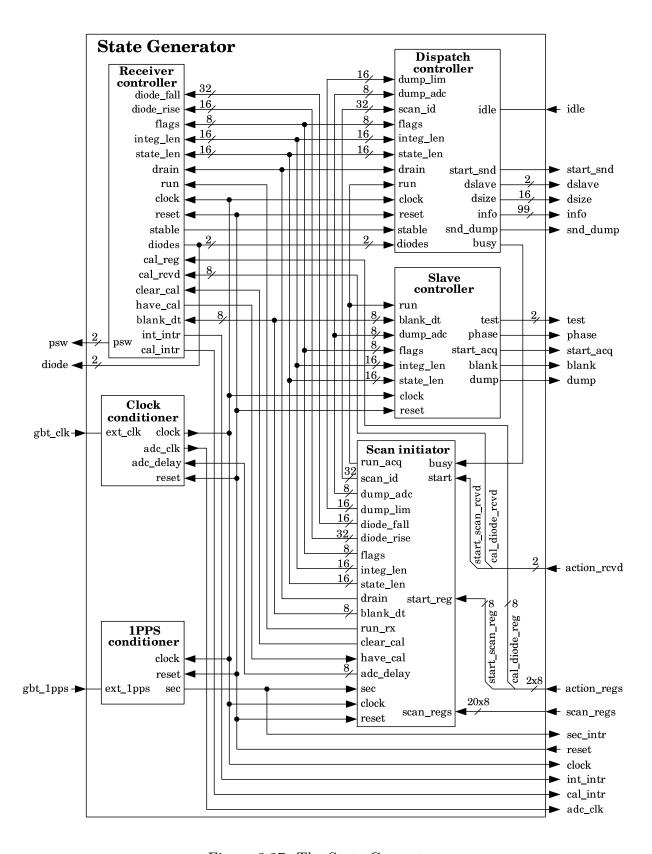

|          | 3.3  | The S  | tate Generator                          | 63 |

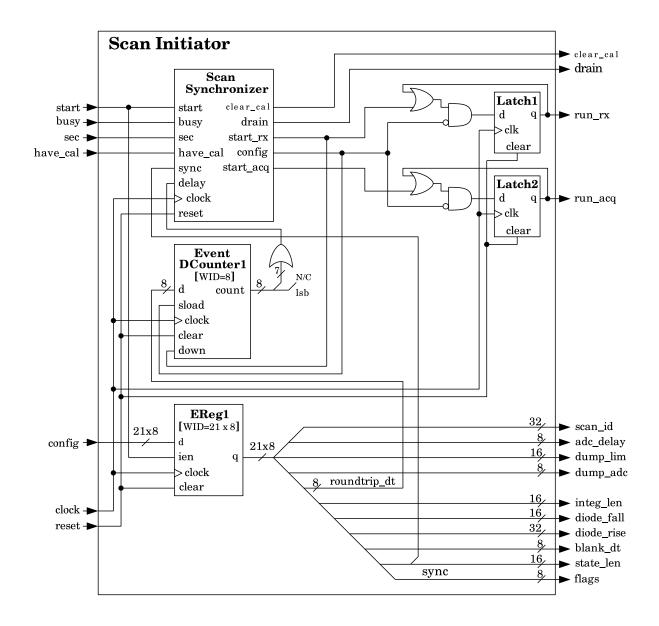

|          |      | 3.3.1  | The Scan Initiator                      | 64 |

|          |      | 3.3.2  | The Receiver Controller                 | 69 |

|          |      | 3.3.3  | The Slave Controller                    | 81 |

|          |      | 3.3.4  | The Dispatch Controller                 | 83 |

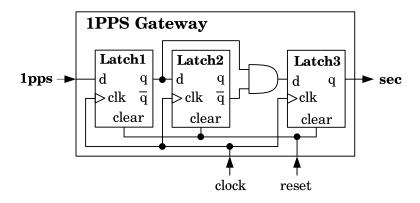

|          |      | 3.3.5  | The 1PPS Gateway                        | 88 |

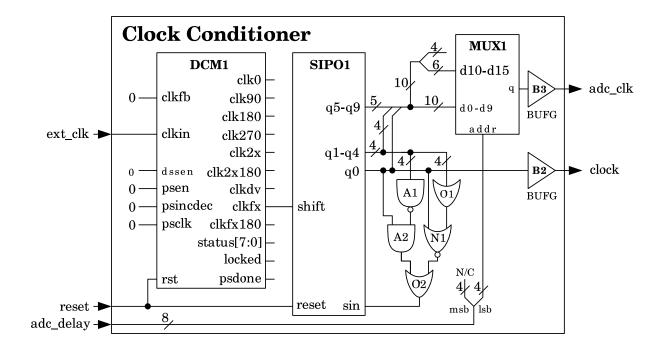

|          |      | 3.3.6  | Clock Conditioner                       | 88 |

|          | 3.4  | Custo  | m generic components                    | 93 |

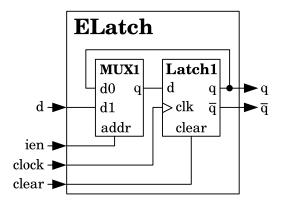

|          |      | 3.4.1  | The ELatch component                    | 93 |

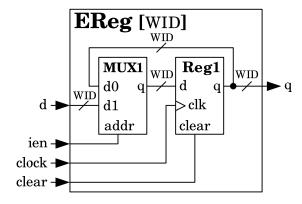

|          |      | 3 4 2  | The EReg component                      | 94 |

| A | CCB cont | rol and configuration registers | 104 |

|---|----------|---------------------------------|-----|

|   | 3.4.7    | The CCB FIFO component          | 100 |

|   | 3.4.6    | The Metronome component         | 100 |

|   | 3.4.5    | The Event DCounter component    | 97  |

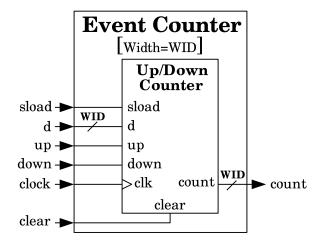

|   | 3.4.4    | The Event Counter component     | 96  |

|   | 3.4.3    | The CCB PISO component          | 94  |

# List of Figures

| 1.1  | An overall summary of the FPGA connections                                                  | 7  |

|------|---------------------------------------------------------------------------------------------|----|

| 2.1  | The top-level design of the slave FPGA                                                      | 10 |

| 2.2  | The Heartbeat Generator component                                                           | 13 |

| 2.3  | The Signal Injector component                                                               | 14 |

| 2.4  | The Sampler component $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$             | 15 |

| 2.5  | The VHDL implementation of the Blanker component                                            | 16 |

| 2.6  | The Integrator component                                                                    | 17 |

| 2.7  | The Accumulator component                                                                   | 18 |

| 2.8  | The VHDL implementation of the Flagger component                                            | 20 |

| 3.1  | The top-level design of the master FPGA                                                     | 22 |

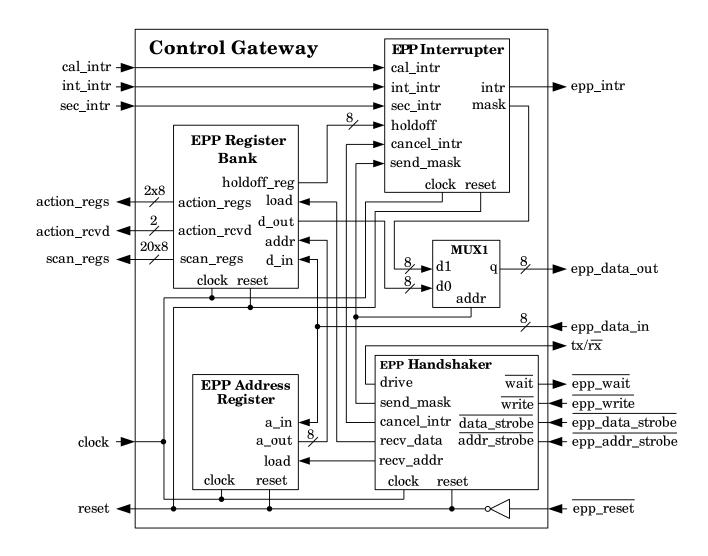

| 3.2  | The Control Gateway                                                                         | 25 |

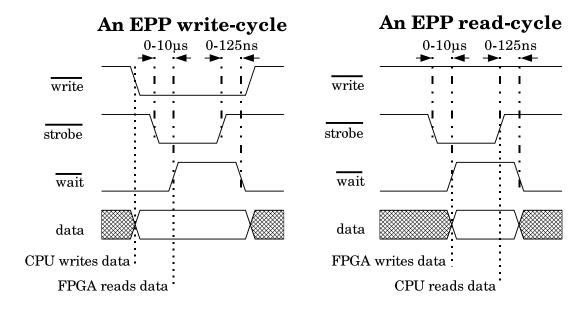

| 3.3  | The standard EPP I/O cycles $\ \ldots \ \ldots \ \ldots \ \ldots \ \ldots \ \ldots$         | 26 |

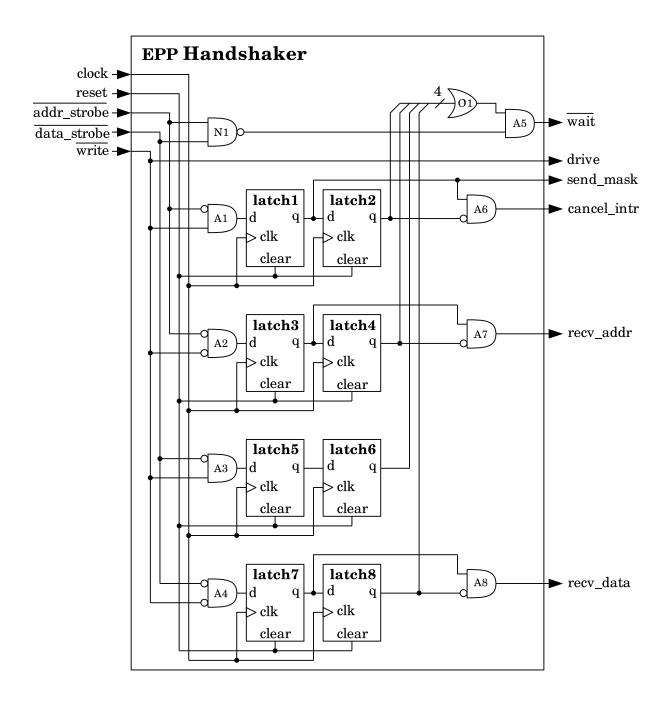

| 3.4  | The EPP Handshaker                                                                          | 28 |

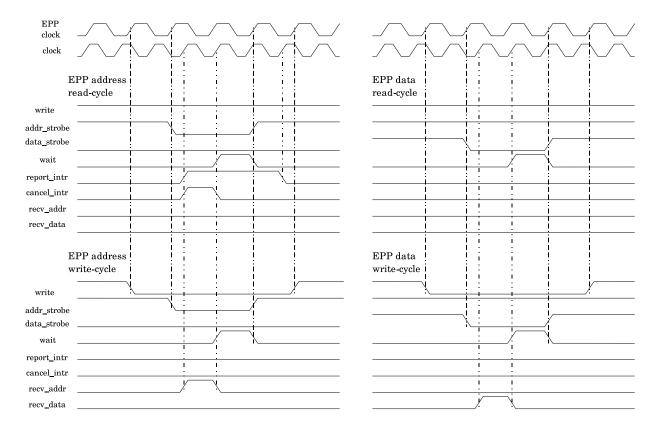

| 3.5  | Timing diagrams of the EPP Handshaker                                                       | 31 |

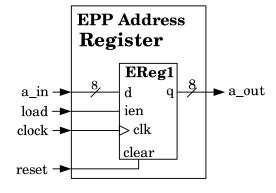

| 3.6  | The EPP Address Register                                                                    | 31 |

| 3.7  | The VHDL implementation of the Register Bank component                                      | 33 |

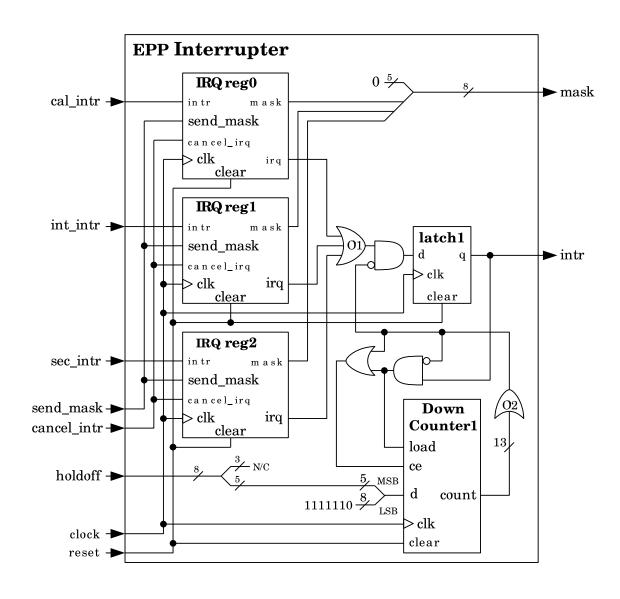

| 3.8  | The EPP Interrupter module                                                                  | 34 |

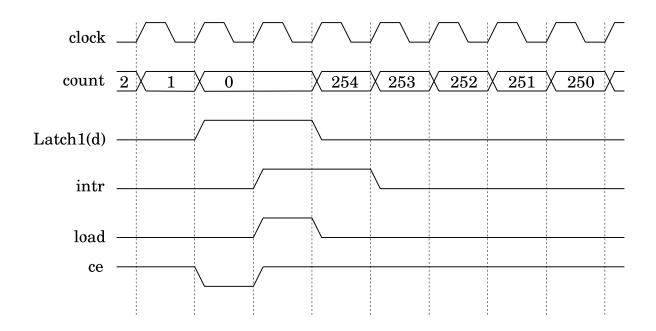

| 3.9  | A timing diagram of the interrupt hold<br>off counter $\ \ldots \ \ldots \ \ldots \ \ldots$ | 35 |

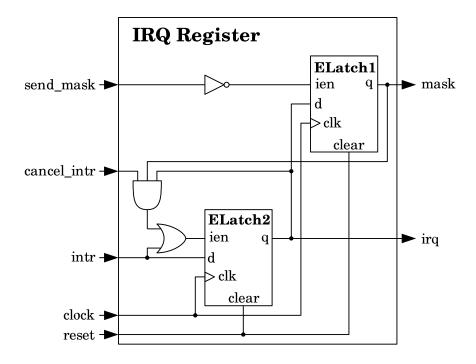

| 3.10 | An Interrupt Request (IRQ) Register                                                         | 36 |

| 3.11 | Timing diagrams of an IRQ Register during an EPP address-read $\ \ldots \ \ldots$           | 38 |

| 3.12 | The Data Dispatcher                                                                         | 41 |

| 3.13 | The Slave Reader                                                                            | 43 |

| 3.14 | The VHDL implementation of the Frame Sizer                                                  | 45 |

| 3.15 | A timing diagram of the Slave Reader                                                        | 46 |

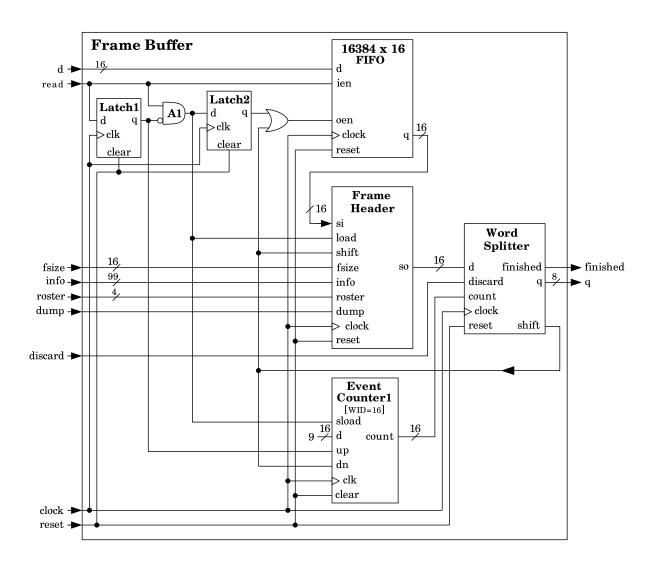

| 3.16 | The Frame Buffer                                                                            | 47 |

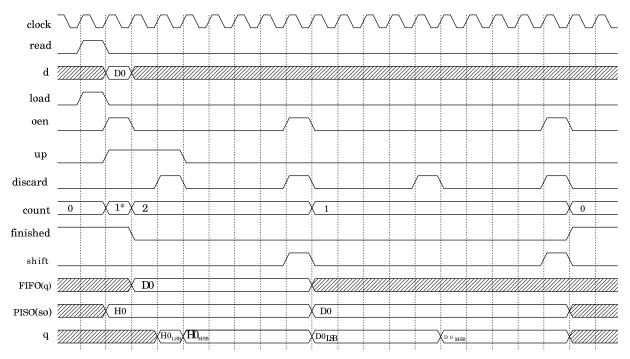

| 3.17 | A timing diagram of the Frame Buffer                                                 | 49  |

|------|--------------------------------------------------------------------------------------|-----|

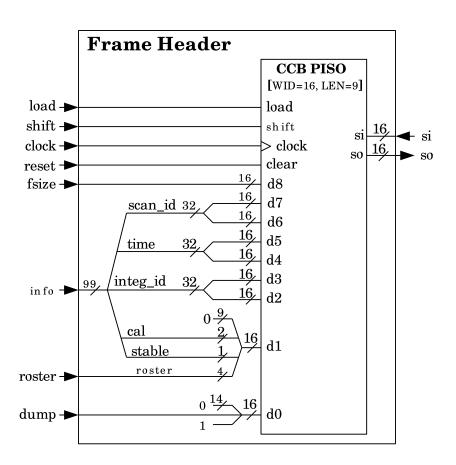

| 3.18 | The Frame Header                                                                     | 50  |

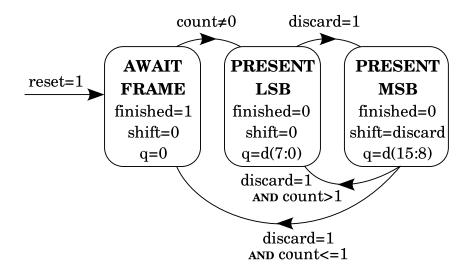

| 3.19 | The state diagram of the Word Splitter FSM                                           | 52  |

| 3.20 | The VHDL implementation of the Word Splitter                                         | 54  |

| 3.21 | The timing specifications of a write-cycle to the USB chip's FIFO $ \ldots  \ldots $ | 55  |

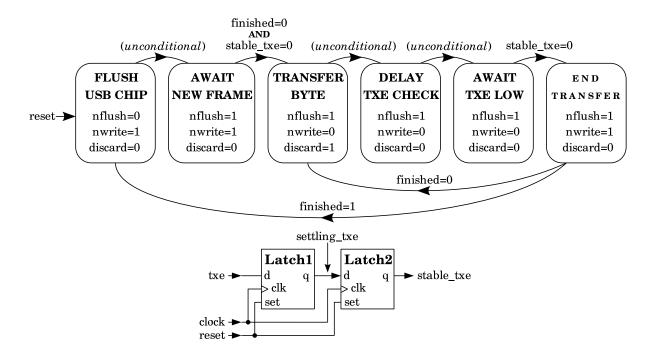

| 3.22 | The state diagram of the Byte Streamer state machine                                 | 55  |

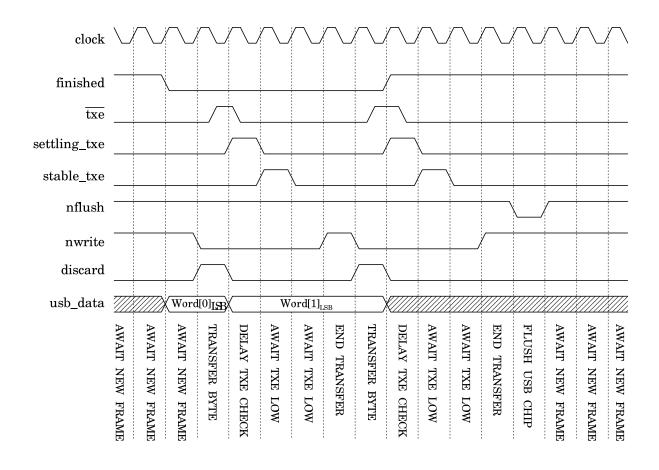

| 3.23 | A timing diagram of the Byte Streamer                                                | 58  |

| 3.24 | The VHDL implementation of the Byte Streamer's state-machine $\ \ldots \ \ldots$     | 59  |

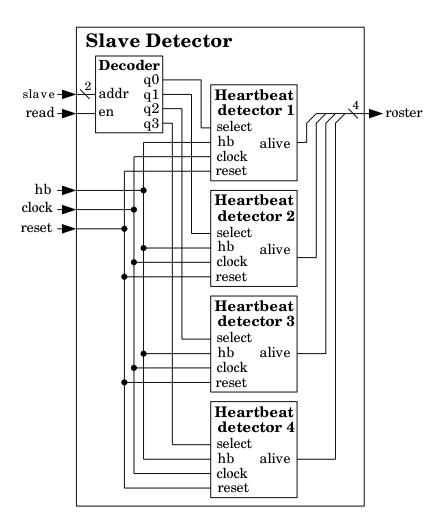

| 3.25 | The Slave Detector                                                                   | 60  |

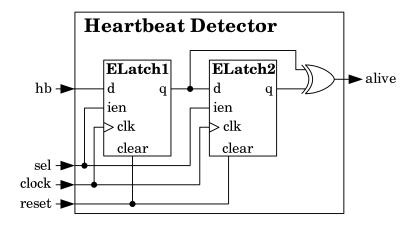

| 3.26 | The Heartbeat Detector                                                               | 61  |

| 3.27 | The State Generator                                                                  | 62  |

| 3.28 | The Scan Initiator                                                                   | 65  |

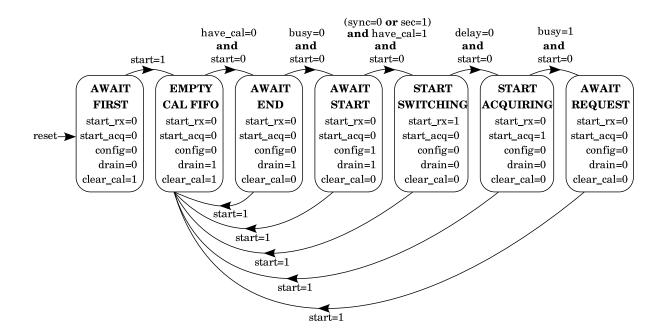

| 3.29 | The state diagram of the Scan Synchronizer FSM                                       | 66  |

| 3.30 | The VHDL implementation of the Scan Synchronizer                                     | 70  |

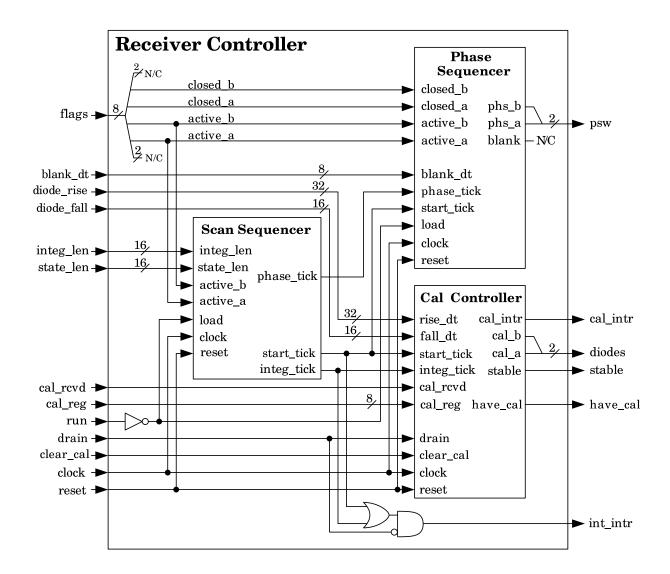

| 3.31 | The Receiver Controller                                                              | 7   |

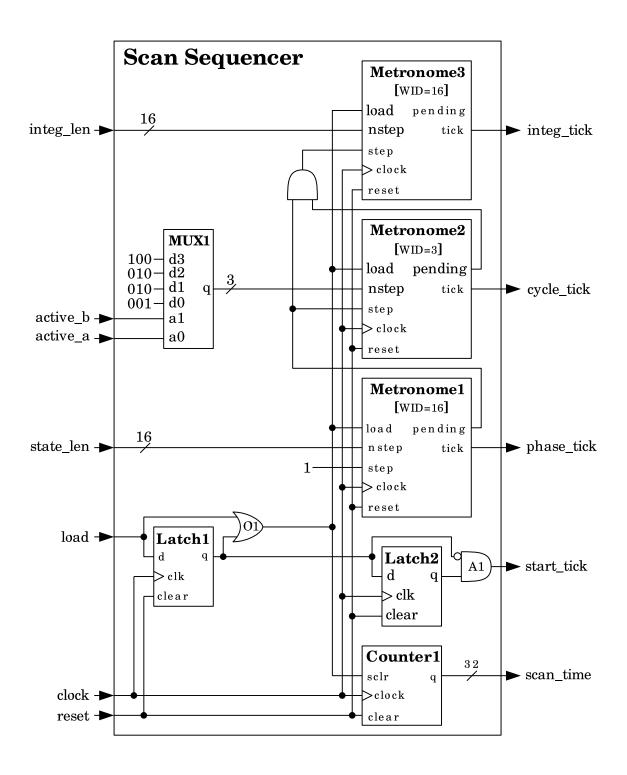

| 3.32 | The Scan Sequencer                                                                   | 73  |

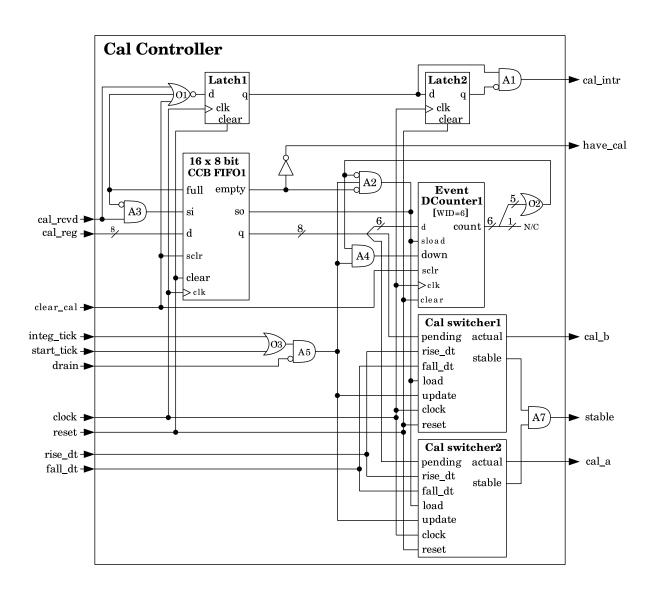

| 3.33 | The Cal Controller                                                                   | 76  |

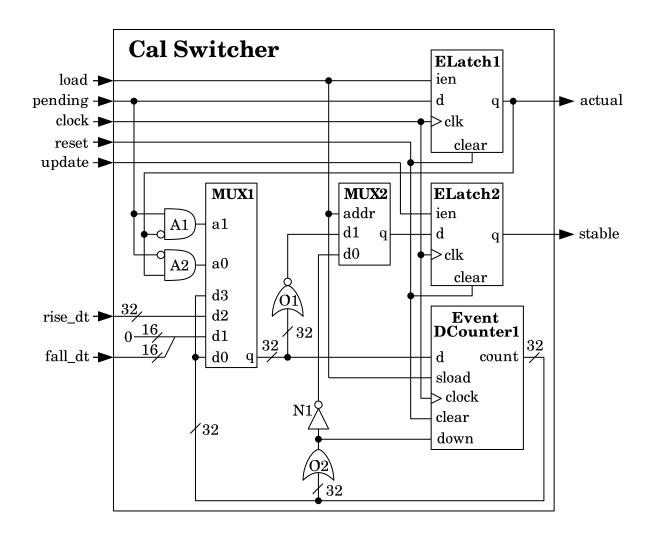

| 3.34 | The Cal Switcher                                                                     | 78  |

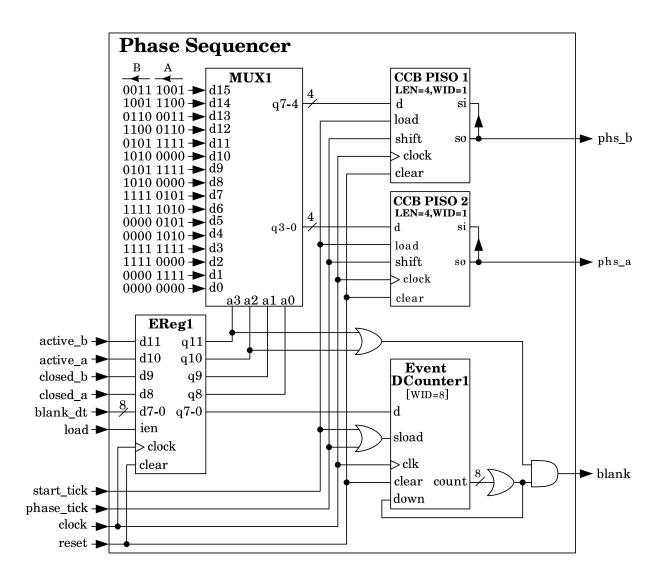

| 3.35 | The Phase Sequencer                                                                  | 80  |

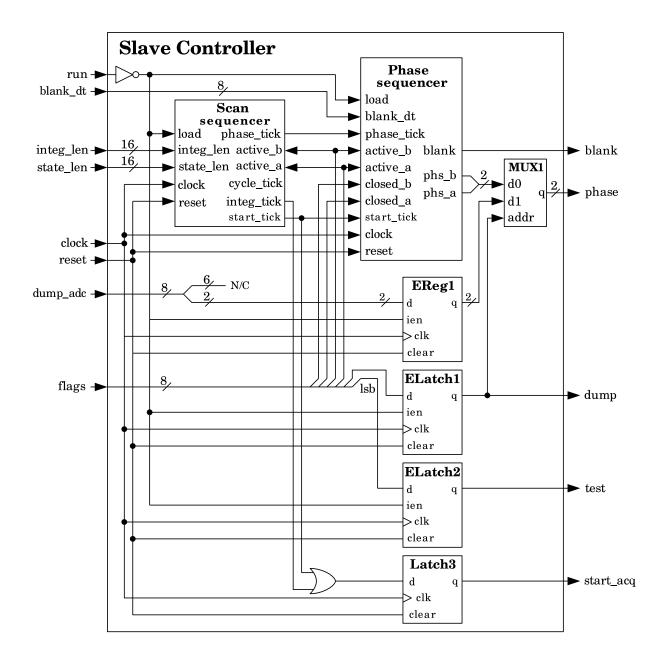

| 3.36 | The Slave Controller                                                                 | 82  |

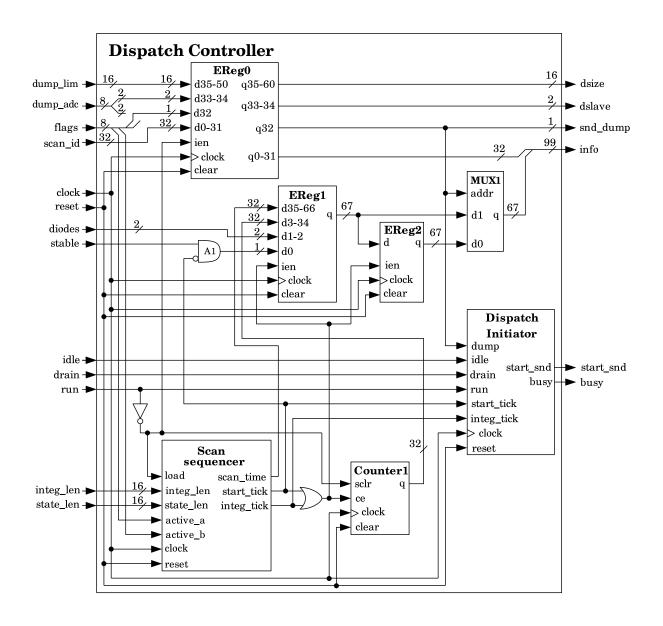

| 3.37 | The Dispatch Controller                                                              | 84  |

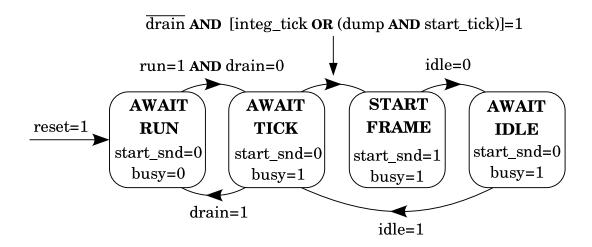

| 3.38 | The state diagram of the Dispatch Initiator FSM                                      | 86  |

| 3.39 | The VHDL implementation of the Dispatch Initiator                                    | 89  |

| 3.40 | The 1PPS Gateway                                                                     | 90  |

| 3.41 | The Clock Conditioner                                                                | 90  |

| 3.42 | A D-type latch with a synchronous input-enable input                                 | 94  |

| 3.43 | A register with a synchronous input-enable input                                     | 94  |

| 3.44 | One node of a CCB PISO component                                                     | 95  |

| 3.45 | An example 4-node 2-bit wide CCB PISO component                                      | 96  |

| 3.46 | An up/down counter with synchronous parallel load capability                         | 9   |

| 3.47 | A VHDL implementation of the Event Counter component                                 | 98  |

| 3.48 | A VHDL implementation of the Event DCounter component                                | 99  |

| 3.49 | The VHDL implementation of the Metronome component                                   | 101 |

| 3.50 | The VHDL implementation of the CCB FIFO component | 103 |

|------|---------------------------------------------------|-----|

| A.1  | A list of all CCB registers                       | 105 |

## Chapter 1

## Introduction

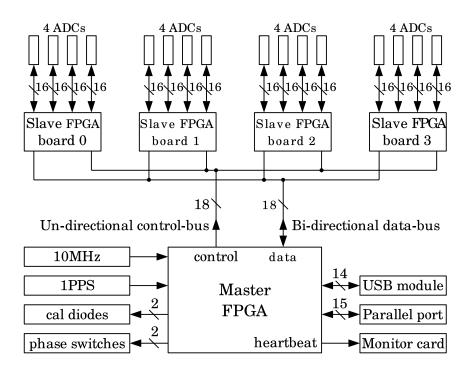

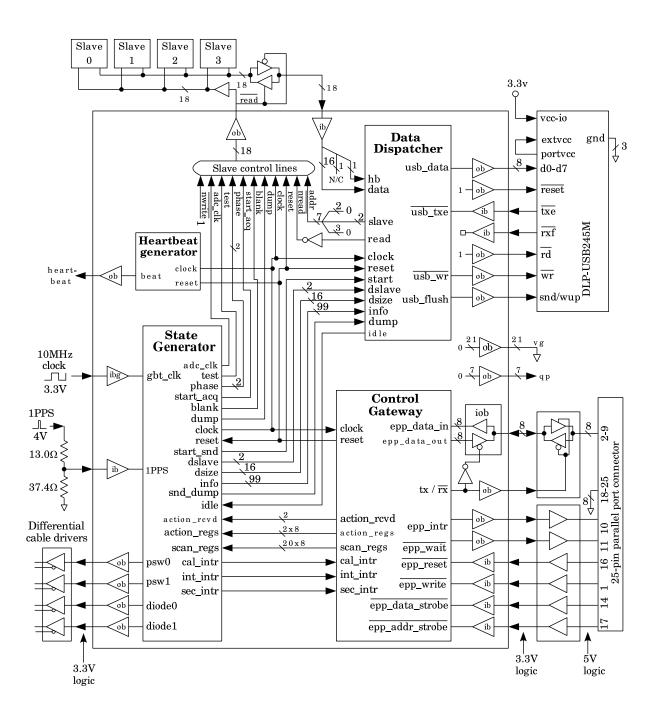

Figure 1.1: An overall summary of the FPGA connections

Figure 1.1 shows the overall architecture of the FPGAs with respect to the rest of the CCB. At the heart of the system, the master FPGA controls 4 slave FPGAs, communicates with a host computer via a USB link and an EPP-enabled parallel port, and generates signals that control the calibration diodes and phase switches in an external differential radiometer. All of its timing signals are derived from the Green Bank 10MHz and 1PPS reference signals.

There are 16 ADCs in the CCB, partitioned equally between the four slave FPGAs. Each

slave FPGA simultaneously clocks out 14-bit samples from its 4 ADCs, at a continuous 10MSPS, and either integrates these samples until told to deliver the integrations to the master FPGA, or is told to deliver them individually to the master FPGA. In either case, the resulting data are first streamed to the master FPGA, over the master-slave data-bus, and are then streamed to the computer via the USB link. Note that although the master-slave data-bus is bi-directional, the CCB treats it as a uni-directional bus, directed from the slaves to the master FPGA. The slave FPGAs use 16 bits of the 18-bit bus to send integrated or raw data to the master FPGA and 1 bit to send a heartbeat signal to the master FPGA. This leaves one bit currently unused.

The EPP parallel-port is used by the host computer to send configuration information and commands to the master FPGA, as well as to acknowledge interrupts that the master FPGA generates on the EPP-port's interrupt pin. The host computer can also optionally read back configuration values over the same link.

The following two chapters detail the internal logic and external interconnections of the Slave and master FPGAs, respectively.

## Chapter 2

### The slave FPGAs

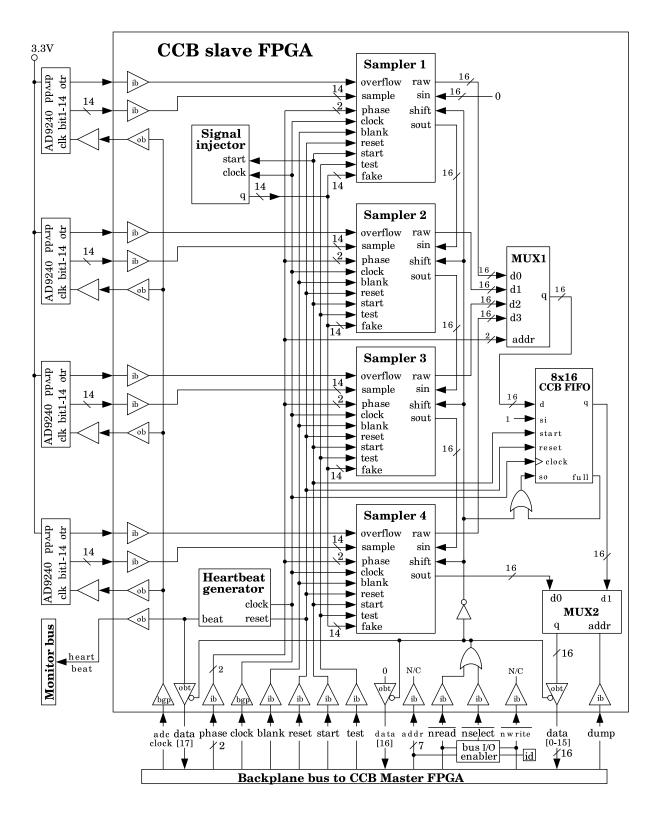

There are 4 slave FPGAs controlled by one master FPGA. All of the slave FPGAs are identical, so this chapter documents the internal components, and external I/O connections of a single slave FPGA. Figure 2.1 shows the layout of a slave FPGA, showing the major logic components within the FPGA, the internal interconnections between these components, and all of the external I/O-pin connections to the 4 ADCs to the left, and to the master FPGA, via the backplane bus, at the bottom of the diagram.

### 2.1 An overview of the internals of a slave FPGA

Starting from the left hand-side of the diagram, the adc\_clock input is a phase-shifted copy of the main FPGA clock-signal. This signal clocks the 4 external ADCs, whose outputs are then latched by the main FPGA clock-signal, clock, into input registers within the associated Sampler components. The configurable phase shift between the adc\_clock and clock signals allows one to control at what point in each ADC sampling cycle the FPGA latches samples from the ADCs, and thus allows one not only to accommodate the relative timing requirements of the ADCs and the FPGAs, but also to move the noisy active part of the FPGA clock cycle away from critically sensitive parts of the ADC clock cycle.

Next, the *Sampler* components take either the latched ADC samples, as their input samples, or fake pseudo-random samples from the *Signal Injector* component, according to the state of the test control-signal. The selected input samples are then presented at the raw outputs of the *Sampler* components, as well as being integrated.

Within the individual *Sampler* components, each new sample is integrated by adding it to one of 4 phase-switch bins. The appropriate phase-switch bin is specified by the master FPGA, via the phase control input. When the master FPGA commands the start of a new integration period, by asserting the start signal, the contents of the phase-switch bins

Figure 2.1: The top-level design of the slave FPGA

from the previous integration period, are transferred into I/O buffers, ready for transmission to the master FPGA. Simultaneously, within each *Sampler*, the bin that is selected by the phase signal, is initialized with the first ADC sample of the new integration period, while the remaining bins are zeroed.

The I/O buffers of the *Sampler* components, take the form of PISOs (Parallel In Serial Out). The sin inputs and sout outputs of the PISOs within each Sampler component, are chained together to form one long PISO that contains the final integrations of all of the *Sampler* components.

The active-low nselect control-signal is asserted when the addr signal contains the board-ID of the slave, and either of the active-low nread or nwrite strobes is asserted. This tells the slave that the master wishes it to transfer data over the data-bus, in the direction that is indicated by whether the nread signal or the nwrite signal is asserted. In the current design the master never sends anything to the slaves over the data-bus, so the nwrite strobe is simply ignored by the slave FPGAs.

When the nread signal is asserted, the addressed slave responds by sending the master either integrated, or raw ADC samples, depending on whether the dump signal is asserted. The master asserts the nread strobe just after the rising edge of the clock. Until the next clock edge, all that this does is enable the tri-state output buffers of the addressed slave FPGA, to drive the first sample onto the data-bus. One clock cycle later, on the next rising edge of the clock, the data-bus lines are assumed to have settled, so the master FPGA reads the initial sample off the data-bus. At the same time, the PISOs in the Sampler components see the asserted nread strobe, and clock out the next data sample, ready to be read by the master FPGA, another clock cycle later. Subsequently, samples continue to be clocked out on the rising edges of the clock, until the nread strobe is deasserted again by the master.

The asserted nread strobe also causes the addressed slave to drive a bussed copy of its heartbeat signal, data[17], as well as the currently unused data[16] output signal onto the data-bus.

The source of the output data signal of a slave FPGA is determined by MUX2. In normal integration mode, this selects the output of the integration PISO. In dump-mode, it selects one of the raw *Sampler* outputs.

The phase control-signal has different interpretations in the two acquisition modes. In normal integration mode, it identifies the phase-switch bin that the latest sample should be added to, whereas in dump mode it identifies the *Sampler* whose raw samples are to be passed to the data output, via MUX2.

Note that in normal integration mode, new integrations are ready to be read-out from the slave's output PISO on the second rising clock-edge that follows the rising edge of the start signal.

In dump mode, when a pulse at the start input indicates the start of a new integration

period, any existing contents of the CCB FIFO component are replaced with the first raw sample of the integration period. The purpose of this FIFO is to allow the *Data Dispatcher*, in the master FPGA to take a few clock cycles to start reading out raw samples, without missing the corresponding number of samples at the start of the integration period. If the master FPGA takes more than 8 clock cycles to read the first sample from the FIFO, then the full output of the FIFO causes the first sample of the integration period to be shifted out, as though it had been read by the master FPGA, and thus frees up room for the latest raw sample to be shifted in. Thus the master FPGA has 8 clock cycles to start reading out dump-mode raw samples from the slave.

All input and output signals from the slave FPGA have to pass through buffers in the FPGA's I/O blocks. These buffers are shown in the diagram. Buffers marked ib are Xilinx ibuf input buffers, those marked ob are Xilinx obuf output buffers, those marked bgp are Xilinx bufgp global-clock-network input buffers, and those marked obt are Xilinx obuft tri-state output buffers. All of these buffers have been explicitly configured to accommodate the 3.3v low-voltage CMOS I/O standard. To maximize the number of outputs that can be simultaneously switching, without causing excessive ground-bounce, the output buffers have also been configured to use the lowest supported drive current, and the slowest supported slew time.

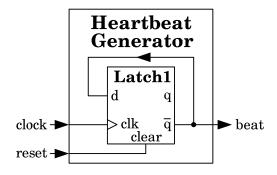

### 2.1.1 The Heartbeat Generator

The slave FPGAs generate a clock-like heartbeat signal that has two uses.

- 1. The external PC104 based monitoring system generates a leaky average of the heartbeat output signal, for monitoring by the computer. When the heartbeat signal is operating correctly, this average should be around half of the full-scale digital high voltage.

- 2. The heartbeat signal is also driven onto the master-slave data-bus, whenever the slave is selected, so that the master FPGA can determine if that slave is present and showing signs of life.

The circuit that generates the heartbeat signal is shown in figure 2.2. This generates a signal whose state alternates at the start of each FPGA clock cycle. It thus looks like a 5MHz clock signal, whose edges are synchronous with the main 10MHz clock signal.

When a particular slave FPGA is selected for readout, the master FPGA latches a copy of its heartbeat signal at the start of each clock cycle, and keeps the latched values from the two most recent successive clock cycles. Since the state of the heartbeat signal should alternate from one clock cycle to the next, the master FPGA then compares the two states with an XOR gate. If the two successive states aren't opposites, then the originating slave is flagged in the output data that are sent to the CCB computer.

Figure 2.2: The Heartbeat Generator component

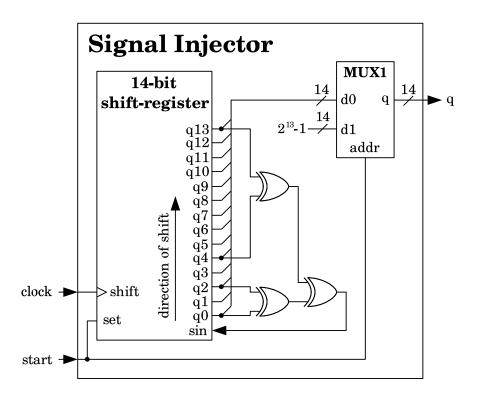

### 2.1.2 The Signal Injector

The job of the Signal Injector is to generate repeatable pseudo-random fake ADC samples, that can be used in place of real ADC samples. The implementation, as shown in figure 2.3, is essentially a conventional linear-feedback shift-register, configured to generate 14-bit random positive integers. The sequence of random numbers repeats every  $2^{14} - 1$  clock cycles, and within this period, each number between 1 and  $2^{14} - 1$  is generated exactly once. To ensure that the results are repeatable for each integration, the sequence is re-started whenever the master FPGA asserts the start signal. This is done by asserting the set input of the shift-register, which sets all of the bits of the shift-register to 1. The first number of the new sequence is ready to be latched on the rising clock edge that follows the falling edge of the start signal. This is unfortunately one clock cycle too late for the integrators, which latch their first sample during the same rising clock edge as the Signal Injector is starting to reset itself. Thus while the Signal Injector is resetting itself, MUX1 substitutes  $2^{13}-1$  for the otherwise unpredictable output value of the shift register. The value  $2^{13} - 1$  was chosen because it is the end value of the pseudo-random sequence, and thus usually precedes the random number sequence returning to its initial value of  $2^{14} - 1$ . Thus, from the point of the integrators, the sequence of fake samples simply starts one number earlier in the circular sequence of pseudo-random numbers.

Note that if the value of the shift-register somehow becomes zero, then the generation of random numbers ceases. However, although glitches could potentially force the register into this state, the correct sequence will be started anew at the start of the next integration period, so automatic restarting hasn't been included. Automatic restarting would be of dubious utility anyway, since this would cause a break the otherwise repeatable test-sequence.

Figure 2.3: The Signal Injector component

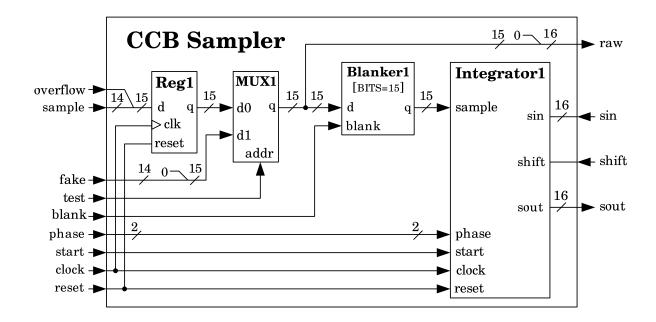

### 2.1.3 The Sampler component

The job of each *Sampler* component is to acquire raw samples from its ADC, integrate either these samples, or fake ADC samples, into phase-switch bins, and present both the resulting integrated values, and the real or fake samples, for collection by the master FPGA. The implementation is shown in figure 2.4.

Register Reg1 uses the global FPGA clock to acquire successive sample and overflow signals from the external ADC. Multiplexer MUX1 then takes either this sample and its overflow, or a fake sample, with no overflow, and presents these to Blanker1 module. Blanker1 module either blanks the sample and overflow signals, by replacing them with zeroes, or presents them unchanged to integrator Integrator1. The integrator then routes the resulting sample and overflow signals to be added to one of its 4 internal accumulators (phase-switch bins), according to the states of the phase switches. The Sampler also taps off a copy of the sample and overflow bits, from before the blanking step, and presents these at the raw output, for dump-mode data-collection.

Within the currently selected accumulator, if an input sample either has its overflow bit asserted, or its addition to the integration would overflow the 32-bit accumulator, then the contents of the accumulator are replaced with a 32-bit number that has all bits set to 1. Thereafter, this state persists until the accumulator is reset for the next integration period.

Figure 2.4: The Sampler component

The start input signal, which the master FPGA asserts for one clock cycle, indicates the end of one integration period, and the start of the next. When this is asserted, the contents of the integration bins are copied into a PISO within Integrator1, and the integration bins are prepared for the new integration. Preparation for the new integration involves initializing the accumulator of the currently selected phase-switch bin, with the output value of Blanker1, and zeroing the accumulators of the remaining 3 phase-switch bins.

Although the outputs of the accumulators are 32 bits wide, the data-bus that connects the slaves to the master FPGA is only 16 bits wide. Thus the PISOs are 16-bits wide, and each integrated sample is split into two parts before being loaded into this PISO, ordered such that the least significant 16-bits emerge from the so output, before the 16 most significant bits. The PISOs within neighboring *Sampler* components are chained via their so and si ports, and when being read-out, they are all simultaneously clocked via their shift inputs.

### 2.1.4 The Blanker component

Blanker components take a multi-bit input signal, d, and either present this unchanged at the q output, or, if the blank input is asserted, set all the bits of the q output to zero. They are trivially implemented by the VHDL code shown in figure 2.5.

```

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity blanker is

generic(BITS: std_logic_vector := 32);

Port ( d : in std_logic_vector(BITS-1 downto 0);

q : out std_logic_vector(BITS-1 downto 0);

blank : in std_logic);

end blanker;

architecture Behavioral of blanker is

begin

blank_bits: for i in BITS-1 downto 0 generate

q(i) \le d(i) and not blank;

end generate blank_bits;

end Behavioral;

```

Figure 2.5: The VHDL implementation of the Blanker component

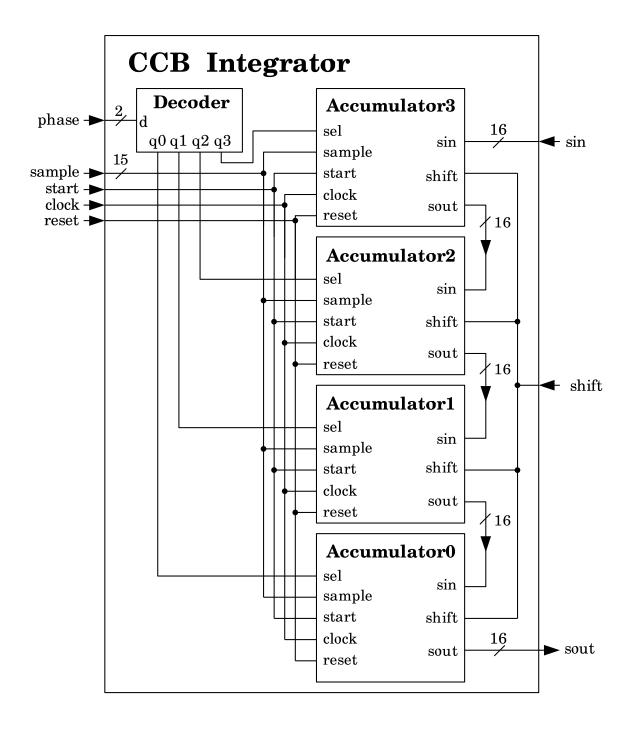

### 2.1.5 The Integrator component

The function of the *Integrator* component has already largely been described in the documentation of the *Sampler* component, so this section just describes its implementation, which is shown in figure 2.6.

Most of the work of an *Integrator* component is performed by four embedded *Accumulator* components, each of which represents one of 4 phase-switch integration bins. Although each new sample is seen by all of the *Accumulator* components, only the *Accumulator* whose sel input is asserted, considers the sample for addition. At the start of each clock cycle, the decoded phase input thus determines which *Accumulator* gets the latest sample. cycle.

The individual *Accumulator* components contain small PISOs that are chained by the parent *Sampler* component, to form the PISO that the parent *Sampler* clocks.

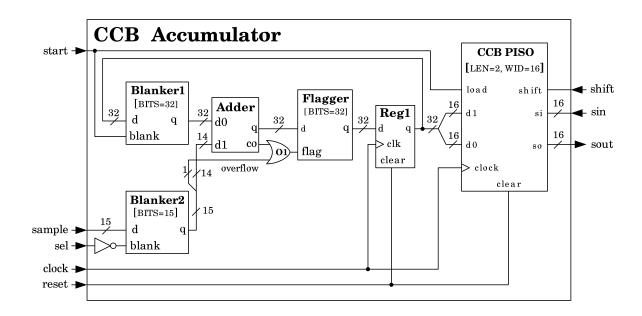

### 2.1.6 The Accumulator component

The *Accumulator* component accumulates the samples of a particular phase-switch integration bin, as described in the documentation of the *Sampler* component. It's implementation is shown in figure 2.7.

In the diagram, the combination of the Adder component and register Reg1, form the ac-

Figure 2.6: The Integrator component

Figure 2.7: The Accumulator component

cumulator cell that is used to integrate samples. This updates every clock cycle, regardless of whether or not the accumulator bin is selected by the parent *Integrator* module. Thus, when the input sample should be ignored, Blanker2 arranges that zero be added, instead of a new sample.

At the start of a new integration period, as indicated by the **start** input being asserted for one clock cycle, Blanker1, which normally feeds back the previous value of the registered output of the adder to the d0 input of the adder, substitutes a value of zero, to discard the previous accumulation. The initial output of the adder thus becomes equal to the value at the d1 input of the adder, which is either equal to the 14 least-significant bits of the sample input, if the accumulator is selected for integration, or to zero otherwise. In the former case, whether the initial sample is then latched from the output of the adder into register Reg1, depends on the state of the overflow bit of the sample, which is the topmost bit of the sample input. If this bit is asserted, then instead of the initial sample value being latched to the accumulator output, the Flagger component initializes the accumulator with the value  $2^{32} - 1$ , which is used to indicate an overflow condition to subsequent analysis software.

By the start of the next clock cycle, the master FPGA has deasserted the start input. On this and subsequent clock cycles, the accumulator continues to behave as already described for the initial clock cycle of the integration period, except that the registered output of the adder is fed back to the d0 input of the adder, instead of zero.

If the 32-bit adder overflows, or the overflow bit of the sample is set when the *Accumulator* is selected, the registered output of the adder is set to the special value  $2^{32} - 1$  by the Flagger component. This is the largest number that will fit into a 32-bit unsigned integer,

so attempting to add any further non-zero samples to this, causes the Adder component to assert its co output, which causes the Flagger component to reinstate the special value. Similarly, adding a sample whose value is zero, leaves the special value unchanged. Thus once an overflow has occurred, the special value persists at the output of the registered adder, until this value gets discarded by Blanker1, at the start of the next integration period.

The CCB PISO component following the accumulator, is a two-entry 16-bit-wide PISO, used to stream the 32-bit output of the accumulator, in two 16-bit chunks, to the master FPGA, followed by those of other Accumulator components. This customized PISO component is documented in section 3.4.3. On the first rising edge of the clock that follows the start signal going high, at the start of a new integration, the accumulator register is initialized with the output of the adder, at the same time that the previous output of the accumulator register is being latched into the PISO. One clock cycle later, the output of the PISO will have settled to hold the least significant 16 bits of the accumulated integration. Thus integrated data can safely start to be read out from the accumulators two clock cycles after the start signal goes high.

Thereafter, whenever the **shift** input of the PISO is found to be asserted during the rising edge of the clock, the PISO is clocked to output the next 16-bit chunk. The first time that this happens, the initial output of the PISO is replaced by the 16 most significant bits of the integration. The second time that it happens, the least significant 16 bits of the preceding *Accumulator* in the chain of *Accumulator* PISOs, is presented, etc.

#### The Flagger component

The *Flagger* component takes a multi-bit input signal, d, and either presents this unchanged at the q output, or, if the blank input is asserted, sets all the bits of the q output to one. Its is trivially implemented by the VHDL code shown in figure 2.8.

```

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity flagger is

generic(BITS: std_logic_vector := 32);

Port ( d : in std_logic_vector(BITS-1 downto 0);

q : out std_logic_vector(BITS-1 downto 0);

flag : in std_logic);

end flagger;

architecture Behavioral of flagger is

begin

flag_bits: for i in BITS-1 downto 0 generate

q(i) <= d(i) or flag;

end generate flag_bits;

end Behavioral;

```

Figure 2.8: The VHDL implementation of the Flagger component

## Chapter 3

## The master FPGA

Figure 3.1 shows the layout of the master FPGA, showing its major internal components, along with their interconnections, and all of the external I/O-pin connections to external chips. The *State Generator* component determines the timing and states of all control-signals that go to the other components within the master FPGA, as well as the control-signals that go to the slave FPGAs, and to the receiver. The *State Generator* is in turn told what to do by the computer, via the *Control Gateway* component, which handles all interactions with the parallel port interface. The *Data Dispatcher* component is responsible for sending integrated and dump-mode data to the computer, via the USB interface. Finally, the *Heartbeat Generator*, which is identical to the heartbeat generators of the slave FPGAs, generates a signal that can be monitored by the computer, via a PC104 I/O card.

All input and output signals from the master FPGA have to pass through buffers in the FPGA I/O blocks. These buffers are shown in the diagram. Buffers marked ib are Xilinx ibuf input buffers, those marked ob are Xilinx obuf output buffers, those marked ibg are Xilinx ibufg global-clock-pin input buffers, and those marked iob are Xilinx iobuf tri-state bi-directional buffers. All of these buffers have been configured to accommodate the 3.3v low-voltage CMOS I/O standard.

When many output pins of an FPGA simultaneously go high or low, the resulting slew currents in the ground pins can cause the effective ground level within the FPGA to significantly rise or fall. This causes otherwise constant voltage levels at input pins to appear to change, and if these changes are sufficiently large, this can generate phantom pulses at asynchronous inputs. To reduce ground-bounce, 21 pins, spread around the FPGA, but marked collectively as vg (virtual ground) in the diagram, are driven low internally, and tied to ground externally. These effectively increase the number of ground-return pins. To facilitate measurements of the ground levels in each of the I/O banks, an additional pin per I/O bank is driven low internally, but left floating externally. These pins are collectively denoted in the diagram by the name qp, which stands for "quiet pins".

Figure 3.1: The top-level design of the master FPGA

### 3.1 The Control Gateway

The Control Gateway handles all interactions with the CCB computer's EPP parallel port interface. It provides an 8-bit register-based interface for the CPU to use to send commands and configuration data to the State Generator, allows read-back of these same registers, and lets the State Generator interrupt the CPU via the parallel port interrupt line.

In addition, the reset signal of the EPP parallel port can be used at any time by the device driver in the CCB computer, to reset the firmware and the USB chip. This will automatically be done whenever the device driver is newly loaded.

The implementation of an 8-bit register-based interface is simplified by the fact that EPP-enabled parallel ports can generate 8-bit address and data I/O cycles in hardware. The 4 types of bus cycles are interpreted by the CCB firmware as follows:

### • The address-write cycle

The byte that this sends to the FPGA is interpreted as the address of one of the registers in the CCB master FPGA. Subsequent data-read and data-write cycles read from and write to the addressed register.

#### • The data-write cycle

The byte that this sends to the FPGA, is copied into the register that was last selected by an address-write cycle.

#### • The data-read cycle

When the FPGA is asked for a data-byte, it sends the contents of the register that was last selected by an address-write cycle.

### • The address-read cycle

When the FPGA is asked for an address-byte, it sends a byte whose individual bits indicate which FPGA event-sources have requested interrupts since the last time that the computer executed an address-read cycle. This also has the side effect of acknowledging any previously unacknowledged interrupt.

There are two occasions that the computer writes data to the master FPGA registers.

1. To start a new scan, the computer first changes the configuration for the new scan, by writing to the scan-configuration registers, then sends a start-scan command, by writing to the start\_scan\_reg register. This tells the master FPGA to stop the current scan as soon as possible and start the new scan.

When the start-scan command is received, the *State Generator* takes a snapshot of the scan configuration registers, and subsequently uses this snapshot to configure the new

scan. This ensures that the computer can write to the scan configuration registers in any order, and at any time, in the secure knowledge that only the values that pertain when the start-scan command is sent, will ever be used. The snapshot configuration is used to configure the scan during the short period between the end of the previous scan and the start of the new scan. This ensures that between the moment when the start-scan command is received, and the moment when the previous scan actually ends, the operation of the previous scan isn't affected by the new configuration. This is important, because the previous scan doesn't end until any pending data, from that scan, have been safely sent to the computer.

2. Since the on/off states of the calibration diodes potentially change at the start of each new integration period, and the new states need to be known in advance of each integration period, the master FPGA uses a FIFO to hold a time-ordered in-advance list of bytes, whose values specify successive cal-diode states and their durations. To initially fill this FIFO, and thereafter keep it full, the computer writes one such cal-diode configuration byte to the master FPGA, whenever it receives a cal\_intr interrupt from the master FPGA.

The master FPGA generates the first cal\_intr interrupt of a new scan, as soon as the corresponding start-scan command is received. Once the computer has responded to this interrupt, by sending the cal-diode configuration of the first integration period, or periods, then the master FPGA generates a new cal\_intr interrupt, to request the cal-diode configuration that should follow the first. It continues to request cal-diode configuration bytes until the FIFO is full. Thereafter, a new cal\_intr interrupt is sent whenever space becomes available in the FIFO. Since individual cal-diode configuration-bytes last for one or more integration periods, this will happen at most once per integration period.

### 3.1.1 The internals of the Control Gateway

The implementation of the Control Gateway is shown in figure 3.2.

Since only one 8-bit register can be read from or written to by the CPU in a single EPP transaction, it is necessary to send the target address for subsequent read and write operations, as a separate EPP transaction. As previously mentioned, to do this, the CPU uses an EPP address-write transaction to send the 8-bit address of the target register. On receiving such an address, the *Control Gateway* stores it in the *EPP Address Register*. Thereafter the output of the *EPP Address Register* is used by the *EPP Register Bank*, to route any subsequent EPP data transactions to the specified register.

The EPP Interrupter allows multiple event-sources in the FPGA to share the single parallel-port interrupt line. When the CPU receives a parallel-port interrupt, it responds by performing an EPP address-read, which both acknowledges the interrupt, and asks the FPGA which event-sources requested the interrupt. The EPP Interrupter, which is told about the

Figure 3.2: The Control Gateway

address-read by the *EPP Handshaker*, responds by sending the CPU an 8-bit interrupt mask, whose individual bits indicate which event-sources have requested interrupts since the last time that the mask was read by the CPU.

The EPP Interrupter has a holdoff input, whose value determines the minimum number of clock cycles to wait between sending one interrupt, before sending another. This prevents interrupts from being sent too frequently for the CPU to handle, and also sets the rate at which unacknowledged interrupts are to be re-sent. If the computer fails to acknowledge receipt of an interrupt within one holdoff interval, a new interrupt pulse is generated. There is no danger that such a re-sent interrupt will be interpreted by the CPU as indicating a second distinct event in the FPGA, since it is the contents of the interrupt mask, rather than the number of interrupts received, that indicates when an event has occurred, and the interrupt mask is automatically cleared as part of the read-address operation.

To avoid a tug-of-war with the CPU, the FPGA only drives the EPP data lines when explicitly requested. Thus the tri-state output buffers in the I/O-blocks of the data pins, and the external data line transceivers are configured to passively receive data from the computer, except when the send signal is asserted.

#### The EPP Handshaker

The *EPP Handshaker* module, as depicted in figure 3.4, is responsible for responding to the standard EPP handshaking signals for all single-byte EPP transfers.

Figure 3.3: The standard EPP I/O cycles

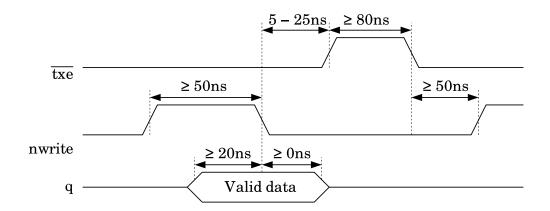

The standard timings of the read and write EPP I/O cycles are shown in figure 3.3. Note

that the strobe signal in this diagram represents either the addr\_strobe or data\_strobe signals, depending on whether an address-write or data-write cycle is in progress, and that the write, data\_strobe, addr\_strobe, and wait EPP signals are all active-low. The write and strobe signals are generated by the computer, while the wait signal is generated by the FPGA. The 8-bit data signal is generated by the computer when performing an EPP write-cycle, and by the FPGA when the computer requests an EPP read-cycle.

When looking at this circuit it is important to note that in order to safely convert an external asynchronous input signal into a synchronous internal signal, it is widely recommended that one use a chain of two latches, to synchronize the signal, instead of just one. The reason is that occasionally the external input signal will violate the setup and hold times of the input latch, and place the input latch in a metastable state. The use of two latches, gives this state an extra clock cycle to resolve itself, before the rest of the circuit sees the synchronized signal.

According to the IEEE-1284 EPP standard, the  $\overline{\text{wait}}$  signal needs to go high either when data written by the CPU have been latched by the peripheral, in the case of a write-cycle, or once data placed on the data lines by the peripheral data have stabilized, in the case of a read-cycle. Due to the above requirement that one use two latches to synchronize an asynchronous input signal, and the fact that data are latched in the FPGA to and from the data lines synchronously with the FPGA clock signal, the minimum delay that we can insert before driving the wait signal high, is up to one FPGA clock cycle between the time that the strobe goes low and the next rising edge of the FPGA clock, plus one extra clock cycle for the synchronization overhead added by the necessary second latch. This delay is thus between 100ns and 200ns, which is well within the maximum of  $10\mu$ s dictated by the IEEE-1284 standard. This minimum delay is what is implemented by the EPP Handshaker. The  $\overline{\text{wait}}$  signal is driven high by the outputs of the rightmost of each pair of latches in the diagram, between one and two FPGA clock cycles after either of the EPP strobe lines goes low. At the corresponding rising edge of the FPGA clock, data are either in the process of being latched by the FPGA, in the case of an EPP write cycle, or are guaranteed to have stable register or interrupt data on them, ready to be read by the CPU, in the case of an EPP read cycle. The implementation of these guarantees will be described shortly.

The wait signal must return low within 125ns of the active strobe signal being returned high by the CPU. This can not be done using synchronous logic, due to the necessary delay of up to two 100ns clock cycles to resolve the potential metastable states caused by the asynchronous strobe signals. Thus the timing of the falling edge of the wait signal is determined by the asynchronous logic formed by gates N1 and A5, which pull the wait signal low as soon as the strobe signal goes low. According to the FPGA's data-sheet, the resulting I/O delays should be less than 10ns, which is clearly well within the maximum of 125ns.

The EPP data lines are handled differently for each of the 4 possible EPP I/O cycles.

### • The EPP address-read cycle

Address-read cycles are used by the CCB host to both acknowledge and receive informa-

Figure 3.4: The EPP Handshaker

tion about which interrupt-requesting events have occurred since the last address-read. The parallel port initiates such cycles, by pulling the addr\_strobe signal low, while holding the write signal high. This causes the input of latch1 to go high, such that on the next rising edge of the FPGA clock, its q output starts to go high, potentially slowed by metastability problems. This output does three things.

- 1. It drives the send\_mask signal high. This deasserts the clock-enable input of the output latch of the *EPP interrupter*, and thus prevents that latch output from changing its value at the next rising edge of the clock (by which time any metastable state should have resolved itself). This output signal remains asserted, until one clock cycle after the strobe goes low again, and thus ensures that the interrupt mask that is driven onto the data lines remains stable until the CPU has read it.

- 2. It also drives the cancel\_intr signal, which drives the clock-enable input of a different latch in the *EPP interrupter* to clear the interrupt condition that is being reported. Again, this isn't seen until the next rising edge of the clock, such that any metastable state has time to resolve itself.

- 3. Finally, the output of latch1 also drives the input of latch2, whose output both drives the wait signal high, and deasserts the temporarily raised cancel\_intr signal.

Thus, the send\_mask output becomes asserted within one clock cycle of addr\_strobe going low, and subsequently becomes deasserted within one clock cycle of addr\_strobe returning high.

One clock cycle after the **send\_mask** output is asserted, the **wait** signal is driven high, to tell the CPU that the data-lines are presenting stable data to be read.

Just like the <u>send\_mask output</u>, the <u>cancel\_intr</u> output becomes asserted within one clock cycle of <u>addr\_strobe</u> going low, but unlike the <u>send\_mask output</u>, it then remains asserted for precisely one clock cycle, regardless of when <u>addr\_strobe</u> returns high.

Throughout the cycle, the write signal is also routed directly to the drive output, to enable the transmit buffers to drive the data onto the EPP data lines.

#### • The EPP address-write cycle

EPP address-write cycles are used by the CCB to send the address of the CCB register that will next be read from or written to. They are initiated by the CPU by pulling both the addr\_strobe and write lines low. This causes the input of latch3 to go high, and on the following rising edge of the FPGA clock, the output of latch3 starts to go high, possibly delayed by any metastability problems. This, in turn does two things.

1. It drives the recv\_addr signal high. This drives the clock-enable input of the EPP Address Register, such that one clock cycle later this register latches the contents of the data lines.

2. It drives the input of latch4, whose output both drives the wait signal high, and deasserts the recv\_addr signal.

Thus the recv\_addr signal is asserted for one clock cycle, starting up to one clock cycle after the write and addr\_strobe signals go low, and the wait signal goes high one clock cycle later.

#### • The EPP data-read cycle

EPP data-read cycles are used by the CCB to read-back the value of the currently addressed CCB register. The CPU initiates such a cycle by pulling the data\_strobe line low, while the write signal is high. In this case, the circuit doesn't need to tell the rest of the Control Gateway about the transaction, because the default value of the data-bus output of the Control Gateway is the value of the currently addressed register, and since register values can only change during EPP write transactions, there is no need to explicitly freeze this register during a read. Thus, latches 5 and 6 simply respond by driving the wait signal high between one and two clock cycles after the data\_strobe signal goes low and the write signal is high, at which time the CPU can safely read the register value from the data lines. The output is driven onto the EPP data-bus by way of the tri-state output buffers that are enabled by the write signal, routed to them via the drive output.

### • The EPP data-write cycle

EPP data-write cycles are used by the CCB to write values into the currently addressed CCB register. They are initiated by the CPU by driving both the data\_strobe and write signals low. This has the same effect on the recv\_data output as previously described for the address-write cycle. In particular, the recv\_data signal is asserted for one clock cycle, at the end of which the currently addressed register latches the contents of the EPP data lines, just as the wait signal is raised to tell the CPU that the data have been received.

The response of the *EPP Handshaker* to the 4 I/O cycles is illustrated in the timing diagrams of figure 3.5.

#### The EPP address register

The EPP Address Register, as shown in figure 3.6, holds the address of the target data-register of subsequent EPP data-write and data-read cycles. It is implemented using an 8-bit register with a synchronous enable-input, ien (see section 3.4.2). At the start of most clock cycles, the enable input is not asserted, so the register retains its current value. However, when the load input indicates that an EPP address-write transaction is in progress, the asserted ien input of EReg1, causes the signals on the EPP data lines (at the a\_in input) to be loaded into the register.

Figure 3.5: Timing diagrams of the EPP Handshaker

Figure 3.6: The EPP Address Register

The a\_out output is permanently connected to the addr input of the *EPP Register Bank* module, and thus specifies which register in the bank of registers, is to be addressed in subsequent data-register I/O transactions.

#### The EPP Register Bank

The *EPP Register Bank*, whose VHDL implementation is shown in figure 3.7, contains the registers that are used to record and provide read-back of configuration parameters and commands sent by the CPU. It also supplies a read-only CCB identification byte in EPP register 0. The addr input, which comes from the *EPP Address Register* module, selects which register should present its contents at the d\_out output, and which register should latch a new value from the d\_in input, when an EPP data-write transaction is in progress.

The EPP Register Bank holds 4 distinct groups of registers.

- 1. Register zero is an identification register. This has the arbitrary value of 27. As a basic sanity check, when the device driver on the computer starts running, it attempts to read this register, and verify its value. Note that if the computer attempts to write to this register, the new value will be ignored, and the register will retain its special ID value.

- 2. The interrupt holdoff delay is held in register 1. This is a normal read-write register, but because its value is used locally, within the *Control Gateway*, it's value is separately output to the *Control Gateway*, via the holdoff\_reg argument.

- 3. Action registers are register which are written to, to solicit an immediate reaction within the *State Generator*. Examples are the start\_scan\_reg register, which commands the start of a new scan, when written to, and the cal\_diode\_reg register, which adds a new value to the queue of calibration configurations, when written to. Whenever one of these registers is written to by the computer, the corresponding bit in the action\_rcvd output signal, is asserted for one clock cycle, to tell the *State Generator* to perform the associated action. Note that this ensures that the *State Generator* notices the write operation, even if the value of the register stays the same.

- Action registers, and their receipt-notification signals, are passed to the *State Generator* via the action\_regs and action\_rcvd signals.

- 4. Scan configuration registers hold configuration values for the next scan. Changes to their values are not noticed by the *State Generator* until the next time that the computer writes to the **start\_scan\_reg** register. Thus the configuration of the next scan can be sent before the previous scan has ended, without affecting it, and multi-byte registers can be written, one byte at a time, without any danger of a partially changed configuration value being unexpectedly used.

- Scan configuration registers are presented to the *State Generator* via the scan\_regs output.

```

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity epp_register_bank is

generic (NID: integer := 1;

-- The number of identification registers.

NLOCAL: integer := 1; -- The number of control-gateway registers.

NACTION: integer := 2; -- The number of action registerss.

WID: integer := 20; -- The number of scan-config registers.

WID: integer := 8); -- The number of bits per register.

Port (clock, reset : in std_logic;

-- When high, assign d in to the addressed register.

load : in std logic:

-- The byte to assign when load is asserted.

d_in : in std_logic_vector(WID-1 downto 0);

-- The address of the target register.

-- The current value of the addressed register.

addr : in std_logic_vector(WID-1 downto 0);

d_out : out std_logic_vector(WID-1 downto 0);

holdoff_reg : out std_logic_vector(WID-1 downto 0);

-- The value of the interrupt-holdoff register.

action_regs : out std_logic_vector((WID*NACTION)-1 downto 0); -- The values of the action registers.

scan_regs : out std_logic_vector((WID*NSCAN)-1 downto 0); -- The values of the scan-configuration registers.

action_rcvd : out std_logic_vector(NACTION-1 downto 0)); -- The receipt-notification signals of the action registers.

end epp_register_bank;

architecture Behavioral of epp_register_bank is

constant NREG : integer := NID + NLOCAL + NACTION + NSCAN;

constant ID_REG_ADDR : integer := 0;

-- Total number of registers.

-- The address of the CCB identification register.

constant HOLDOFF_REG_ADDR : integer := 1;

-- The address of the interrupt-holdoff register.

constant CCB_ID_VALUE : std_logic_vector(WID-1 downto 0) := "00011011"; -- The value of the CCB identification register.

-- The zero-valued byte, used to initialize registers.

constant REG_ZERO : std_logic_vector(7 downto 0) := (others => '0');

-- Create the array of registers.

type regarray is array (NREG-1 downto 0) of std_logic_vector(WID-1 downto 0);

signal regbank : regarray;

-- Create an internal array of per-register received signals.

signal regrcvd : std_logic_vector(NREG-1 downto 0);

-- An integer version of the addr input.

signal reg_addr : integer range 0 to NREG;

begin

-- Convert the addr argument to an integer, for use as an array index.

reg_addr <= conv_integer(addr) when conv_integer(addr) < NREG else 0;</pre>

-- Export the value of the currently addressed register at d_out.

d out <= regbank(reg addr):

-- Export the value of the holdoff register at the holdoff output.

holdoff_reg <= regbank(HOLDOFF_REG_ADDR);

-- Export the values of the action registers and their notification signals.

EXPORT_ACTION_REGS: for i in 0 to NACTION-1 generate

action_regs(((i+1)*WID)-1 downto i*WID) <= regbank(NID+NLOCAL+i);</pre>

action_rcvd(i) <= regrcvd(NID+NLOCAL+i);

end generate EXPORT_ACTION_REGS;</pre>

-- Export the values of the scan configuration registers.

EXPORT_SCAN_REGS: for i in 0 to NSCAN-1 generate

scan_regs(((i+1)*WID)-1 downto i*WID) <= regbank(NID+NLOCAL+NACTION+i);

end generate EXPORT_SCAN_REGS;

write_reg_proc: process (clock, reset) -- Perform register assignments.

if reset = '1' then

-- Active-high asynchronous reset.

regbank(ID_REG_ADDR) <= CCB_ID_VALUE;

regbank(NREG-1 downto 1) <= (others => REG_ZERO);

elsif clock'event and clock = '1' then -- Rising clock edge

if load='1' and reg_addr /= ID_REG_ADDR then

regbank(reg_addr) <= d_in;

-- Assign a new register value.

regrcvd(reg_addr) <= '1';

-- Flag the register as updated.

else

regrcvd <= (others => '0');

-- Deassert any register update flag.

end if;

end if;

end process write_reg_proc;

end Behavioral;

```

Figure 3.7: The VHDL implementation of the Register Bank component

To synchronously write a new value into the currently addressed register, the new value is first presented at the d\_in input, then the load input is asserted for one clock cycle.

The list of defined registers can be found in appendix A.

### The EPP Interrupter

The implementation of the *EPP Interrupter* module is shown in figure 3.8.

Figure 3.8: The EPP Interrupter module

As explained shortly, the CCB FPGA has three sources of interrupt-worthy events, all of which share the single parallel-port interrupt line (intr), under the auspices of the EPP

Interrupter module. As such, the receipt of a parallel-port interrupt by the computer does not necessarily imply the occurrence of any particular new event in the FPGA. What it does tell the computer is that it should perform an EPP address-read to find out which events have occurred since the last time that it performed such a read. The resulting loose association between individual events and parallel-port interrupts, reduces the number of interrupts that the CPU has to handle, and allows a repeat interrupt to be sent if the computer appears to have missed the previous one, without any danger of the computer incorrectly believing that a repeated interrupt represents a new event. Similarly, the only harm that spurious interrupts can do is steal a bit of CPU time, since the bit-mask of events returned by the subsequent EPP address-read, after a bogus interrupt, will indicate that nothing has really happened.

Interrupts are sent to the CPU at most once every  $256 \times (\text{holdoff} + 1)$  clock cycles. In particular, once any interrupt source has requested an interrupt, a new CPU interrupt is sent every time this number of clock cycles have passed, until the computer performs an EPP address-read to get the bit-mask of previously unreported events. Hardwiring a minimum value of 256 clock cycles, ensures that the computer doesn't get swamped with interrupts if the holdoff input is set to a small value. The holdoff countdown is implemented by Down Counter1. This is a down-counter with a synchronous load capability, and a count-enable input (ce) which, when asserted, tells the counter to count down by one at each rising edge of the clock. Figure 3.9 is a timing diagram that illustrates the behavior of the holdoff counter. It shows the case where an interrupt request is pending, and the holdoff input happens to be zero. It can be seen that the diagram would repeat every 256 clock cycles in this case, and that an interrupt of two clock cycles would be raised anew, each time around.

Figure 3.9: A timing diagram of the interrupt holdoff counter

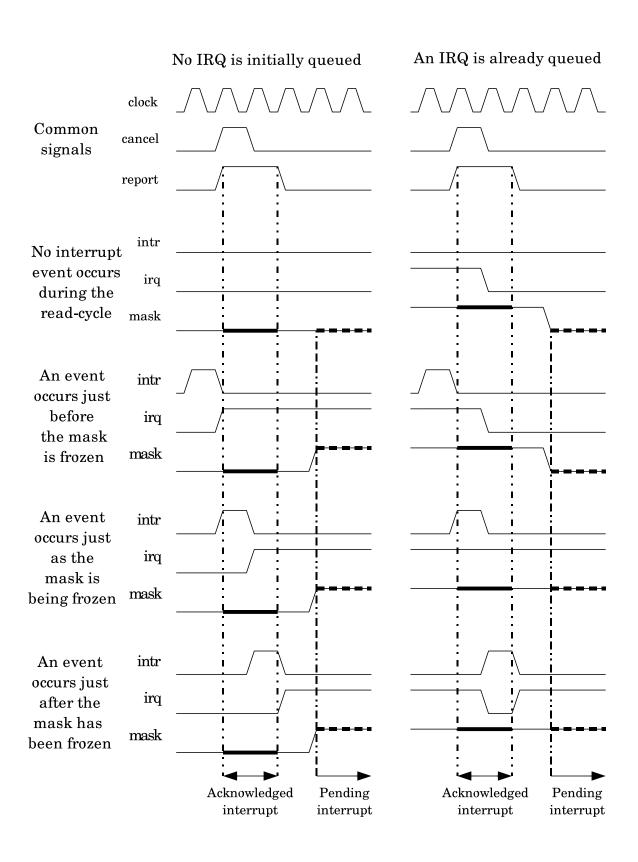

When a particular event-source in the FPGA wishes to notify the computer of a new event, it synchronously asserts the respective one of the cal\_intr, int\_intr or sec\_intr interrupt-request inputs of the EPP Interrupter for one clock cycle. Just after the end of this clock cycle, the corresponding IRQ (interrupt-request) register becomes asserted, and remains asserted until the computer next performs an EPP address-read to query which event-sources have requested interrupts.

The EPP Interrupter examines the irq outputs of the IRQ registers at the start of each clock cycle, and if any of them are asserted, and the hold-off counter isn't still counting down from the previously sent interrupt, then it raises the parallel-port intr signal to interrupt the CPU, and holds this signal high for two FPGA clock cycles (ie. 1.6 EPP 8MHz clock cycles). Simultaneously, it reloads the hold-off down-counter with the number of clock cycles that it should hold-off the generation of the next interrupt.

Figure 3.10, shows the internals of a single IRQ register.

Figure 3.10: An Interrupt Request (IRQ) Register

When the CPU acknowledges the receipt of an interrupt, by performing an EPP address-read, the *EPP Handshaker* asserts the <code>send\_mask</code> input for the duration of the time that the <code>mask</code> output is required to be frozen for reading by the CPU, and it asserts the <code>cancel\_intr</code> input for one clock cycle, to tell the IRQ registers to synchronously forget the sub-set of interrupts that are being reported in the <code>mask</code> output. The register that drive the <code>mask</code> outputs of the individual IRQ registers normally update at the start of each FPGA clock cycle, latching copies of the neighboring <code>irq</code> outputs. The asserted <code>send\_mask</code> input, however, prevents

these updates, by disabling the clock-enable inputs of the mask output registers. Thus, one clock cycle after send\_mask input goes high, when the CPU is first told that it is safe to read the EPP data lines, the mask outputs, along with the EPP data lines that they drive, are guaranteed to have been stable for one clock cycle. Meanwhile, on the clock cycle at which the cancel\_intr input is seen to be asserted, the IRQ registers look at the frozen mask outputs, to see if there is a reported interrupt to be canceled, and if so replace the contents of the registers that drive the irq outputs, with the current value of the intr input. If an interrupt is being requested at that point, this again drives the irq output high, to request a new EPP interrupts. Otherwise, it drives it low, and thus stops that IRQ register from generating EPP interrupts, until the corresponding event-source next asserts its intr input. The aim of this is to guarantee that if any interrupt-worthy event occurs one or more times between two CPU reads of the interrupt mask, the second read will report it to the CPU.

Note that if an event-source requests a new interrupt while its IRQ register is still asserted from a previously unacknowledged request, the new request does nothing. Thus, each bit in the bit-mask of interrupts that are sent to the CPU, only says that one or more of the corresponding event has occurred since the mask was last read. There is no provision for keeping track of how many times the interrupt occurred. A way to keep track of the number of this would be to implement the IRQ registers using up/down counters. New interrupt requests would increment these counters, and acknowledgements would decrement them. The first iteration of the design of the IRQ registers did just this. However, interrupts generally represent events that require a response while the interrupting event is still relevant, so queuing out-dated interrupts is pointless. Furthermore, anytime that EPP interrupts were disabled by the CPU, the CCB would quickly queue hundreds of unacknowledged events. When interrupts were subsequently re-enabled, this would then keep the CPU busy for a while acknowledging stale events. For these reasons, the unnecessarily complex idea of using up/down counters was abandoned, and it was decided that it made more sense to simply design the event-sources and the device driver around a limitation of one queued event per event-source, per EPP address-read.

Figure 3.11 illustrates the behavior of an IRQ register via a timing diagram.

The three interrupt sources that have been implemented, are the following:

#### • cal\_intr - Calibration-diode configuration interrupts.

Before the start of each new integration, the *State Generator* needs to know the desired on/off states of the cal-diodes. In principle this could be sent one integration in advance, from a start-of-integration interrupt handler. That was the original plan. However, to soften the real-time requirements placed on the device driver in the CCB embedded computer, and thereby make the CCB insensitive to occasional transient anomalies in Linux's interrupt latency, a FIFO has been implemented that contains the configurations of many integrations in advance, instead of just one. Keeping this FIFO filled is the job of the cal\_intr interrupt. At the start of a scan, to fill the FIFO,

Figure 3.11: Timing diagrams of an IRQ Register during an EPP address-read

multiple cal\_intr interrupts are generated, each one telling the computer to send one new calibration-diode configuration, for one or more consecutive integrations that are to have the same configuration. Thereafter whenever the oldest configuration in the FIFO is exhausted, that configuration is discarded from the FIFO, and a new entry is requested by sending another cal\_intr interrupt.

The rapid-fire cal\_intr interrupts at the start of a scan are rate-limited in two ways. First, a new cal\_intr input-signal is never raised by the *State Generator* until the CPU responds to the previous one by sending a new cal-diode configuration entry. Secondly, the holdoff timer of the *EPP Interrupter* sets a hard limit on the parallel-port interrupt rate, regardless of how quickly the CPU responds.

#### • int\_intr - Start-of-integration interrupts.

Start of Integration interrupts are sent at the start of each integration period during a scan. In the interval between a start-scan command being received, and the resulting new scan starting, these interrupts cease, starting again at the start of the first integration period of the new scan.

Note that in dump-mode scans, it can take longer than an integration period to dispatch the data that is collected during a single integration period, but start-of-integration interrupts continue to be generated for each consecutive integration period, even if the collection of a new frame of dump-mode data is not started at that time. Thus the number of these events that are reported won't always match the number of data frames sent to the computer over the USB interface.

When a new integration starts before the interrupt from the start of the previous integration has been acknowledged by the computer, the new start-of-integration interrupt request is ignored, but the previous, unacknowledged integration request continues to generate retry interrupts, at intervals controlled by the holdoff timer. Thus the CCB device driver should not count integration interrupts to determine how many integrations have been completed at a given time, and nor should it use this interrupt for anything that absolutely has to be performed within a small time frame following the boundary between 2 integrations.

As mentioned in the discussion of the cal\_intr input, originally, start-of-integration interrupts were needed for sending cal-diode configurations one integration at a time. It isn't clear yet whether this event will be useful for anything else in the device driver, so for the moment, it is included here mostly as a placeholder, and possibly for debugging.

## • sec\_intr - 1 second interrupts.

A sec\_intr interrupt is requested once per second, at the rising edge of the second FPGA clock cycle that follows the rising edge of the pulse of the external 1PPS signal (to avoid metastable latch states). Like the integration interrupt, if a previous 1-second interrupt hasn't been acknowledged by the time that a new one is to be generated, then the new one is simply ignored, while the EPP interrupter continues resending the

original. Given the length of time between these interrupts, this should only happen when the CCB device driver isn't loaded, or if either the parallel cable or the computer are damaged.

By default, at boot time, EPP interrupts are disabled, and a write to the parallel-port's configuration register is needed to enable them. While they are disabled, signals on the intr interrupt line are simply ignored by the computer. Thus the FPGA doesn't redundantly provide its own way to enable and disable the generation of interrupt signals on the intr line. Note that the resending of unacknowledged interrupts every holdoff clock-cycles, ensures that interrupts that are missed while the parallel-port has interrupts disabled, get re-sent and acknowledged once interrupts become enabled.

# 3.2 The Data Dispatcher

In normal integration mode, data that are integrated during each integration period, are ready to be dispatched to the computer at the end of the integration period. In dump-mode, unintegrated data are immediately ready to be sent to the computer, at the start of each integration period. It is the *Data Dispatcher*'s responsibility to collect these integrated or dump-mode data and send them to the computer. In both cases, the *Data Dispatcher* reads the data into a large FIFO, then streams the contents of this FIFO, preceded by a header, to the computer, via the USB bus. All communications over the USB bus are directed from the FPGA to the computer. Thus, although the read (rd) and read-enable (rxf) pins of the USB interface are connected to pins of the master FPGA, there are currently no plans to use them.

Note the use of the DLP-USB245M module. This is a tiny PCB module containing a 6MHz crystal, a surface-mount FT245BM USB1.1 chip, a USB connector and all the interconnections needed between these parts. The PCB is just  $1.5 \times 0.7$  inches in size, and the USB connector sticks out a further third of an inch from one end. The module can be soldered onto the CCB PCB, via 24 dual in-line pins. Its data-sheet can be downloaded from:

http://www.dlpdesign.com/usb/dlp-usb245m12.pdf

The two of these modules that I bought for testing the FT245BM, I got from a company called Saelig (www.saelig.com), which is an official US distributor for the FT245BM. The modules arrived overnight. Since then, I have noticed that Mouser Electronics carries them as well. Their catalog number at Mouser is 626-DLP-USB245M, and they cost \$25.

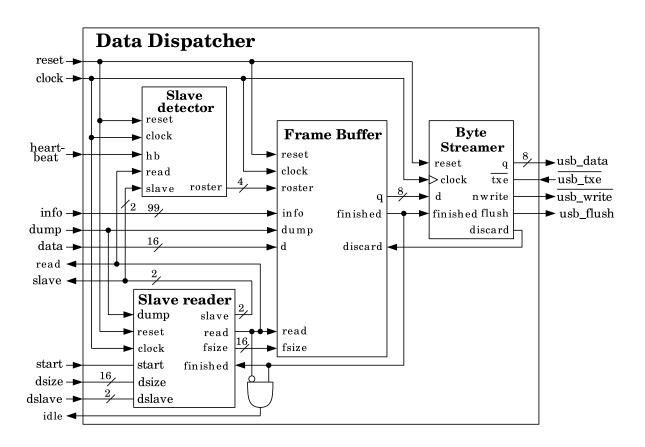

Figure 3.12: The Data Dispatcher

## 3.2.1 The internals of the Data Dispatcher

Figure 3.12 shows the building blocks of the *Data Dispatcher*, and how they are interconnected.

One clock cycle after the start input is asserted, to tell the *Data Dispatcher* to collect and dispatch a new frame of integrated or dump-mode data to the computer, the *Slave Reader* asserts its read output, and keeps it asserted until all available data-samples have been transfered from the slave FPGAs into a FIFO within the *Frame Buffer*. At the rising edges of the clock, this signal is examined both by the *Frame Buffer* and by the currently addressed slave FPGA, and when it is found to be asserted, it causes the transfer of one 16-bit data-sample from the addressed slave to the *Frame Buffer*.

The currently addressed slave FPGA is the one identified by the slave output of the Slave Reader. In normal integration mode, this slave-address is first set to the address of the highest numbered slave FPGA, and then, after all of that slave's samples have been transfered, it is set to that of the next lower numbered FPGA. This continues, until the samples of all of the FPGAs have been transfered to the Frame Buffer. In dump mode, the slave output is persistently given the value of the dslave input, which identifies the slave whose raw ADC samples are to be collected.

Both during and after the period when samples are being read from the master/slave databus into the *Frame Buffer*'s FIFO, the *Byte Streamer* streams the contents of the *Frame Buffer* to the USB interface chip, 8 bits at a time, starting with a header.

Once the contents of the Frame Buffer have been delivered to the USB chip, the finished output of the Frame Buffer is asserted, to tell the Slave Reader that it is okay for it to start collecting a new frame. One clock cycle after this, the USB chip's flush input is strobed low for one clock cycle, to tell it not to wait until it has a full packet, before, before sending any previously buffered data to the computer.

The *Slave Reader* de-asserts its **read** output, to terminate collection of the current data-frame, after the required number of samples have been read from the slaves. In dump-mode, if the number of dump-samples requested by the **dsize** input exceeds the size of the *Frame Buffer*, the *Slave Reader* limits the number of samples to be read, to the actual size of the buffer.

Note that since the *Slave Reader* doesn't allow the collection of a new data frame to be initiated until the *Frame Buffer* indicates that the previous one has been completely sent, and because the *Slave Reader* is careful to halt dump-mode data collection before the FIFO has a chance to overflow, there is no danger, either of gaps in the collected data, caused by temporary overflow conditions, or of a new frame trampling on the contents of a frame that hasn't been fully sent yet.

The idle output signal of the Data Dispatcher is asserted when the Data Dispatcher is not

in the process of either collecting or sending a data-frame to the computer. This is used by the *State Generator* to determine when it is safe to terminate a scan.

#### The internals of the Slave Reader

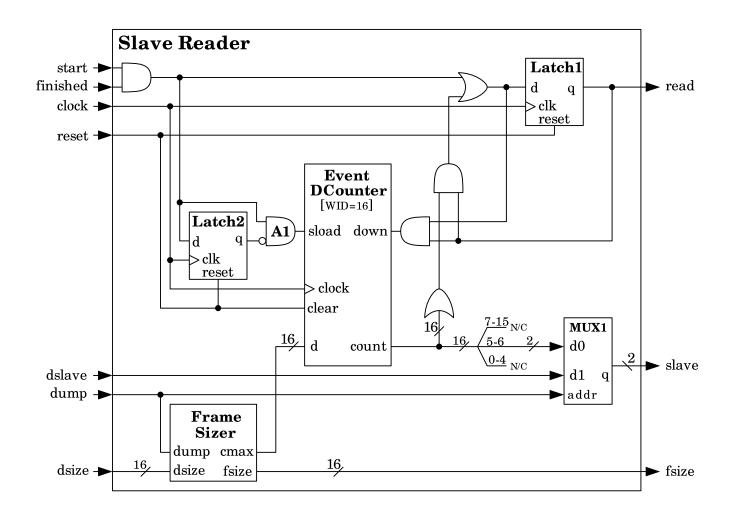

The implementation of the *Slave Reader* is shown in figure 3.13.

Figure 3.13: The Slave Reader

As previously described, the *Slave Reader* selects one slave at a time to write to the data-bus, by way of its slave output, while, at the same time, asserting its read output, to tell both that slave, and the *Frame Buffer*, to transfer one sample over the data-bus, at each rising edge of the clock.

When the finished input signal is asserted, Latch1 and the combinational logic around it, arrange for the read signal to go high, one clock cycle after the start input goes high.

In normal integration mode, this initiates the collection of integrated samples from the preceding integration period. In dump-mode it initiates the collection of raw ADC samples for the integration period that is just starting.

Alternatively, if the finished input signal is still low when the start pulse arrives, this means that the *Frame Buffer* is still busy sending the previous data-frame, and is not ready to start collecting a new frame. When this happens, the low value of the finished input, prevents the *Slave Reader* from seeing the start pulse. As a result, a new data-collection period is not initiated, and the data that would have been collected, are simply discarded.

So, when a start pulse arrives when the finished signal is asserted, although the start pulse only lasts for a few clock cycles (see later), Latch1 and its surrounding logic thereafter hold the read signal high until the countdown of samples remaining to be collected, reaches zero. The read input is then pulled low, to terminate the collection of samples, and thereafter held low until a new start pulse is received.

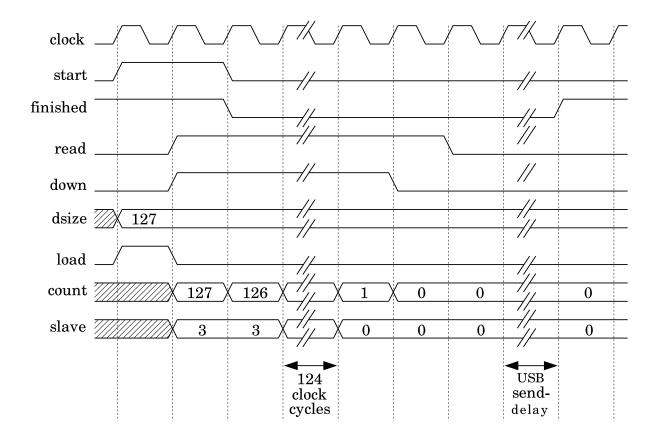

The start pulse, when enabled by the finished input, also loads a down-counter with the number of samples that are to be read. Since the start signal generally is asserted for a few clock cycles, Latch2 and AND gate A1 are used to generate a load pulse that rises asynchronously with the start signal, and then falls on the next rising edge of the clock, after being heeded by the load input. One clock cycle later, the read signal goes high, and the counter starts counting down by one at the start of each clock cycle, until one clock cycle before the read input is due to go low again. This happens when the output count of the counter finally reaches zero, after the requested number of samples have been read.

The number of samples that are to be read from the slaves, is computed by the *Frame Sizer*, whose simple VHDL implementation is shown in figure 3.14.

In normal integration mode, the *Frame Sizer* specifies, via its fsize output, that 128 16-bit words should be read from the slaves. This corresponds to 64, 32-bit integrations, with each sample split into pairs of 16-bit words. In dump-mode, if the value of the dump-lim register, which is presented by the dsize input, is less than or equal to the size of the FIFO in the *Frame Buffer*, then the *Frame Sizer* specifies that this number of samples be read. Otherwise, it specifies the limiting size of the FIFO.

The fmax output of the Frame Sizer is always one less than the value presented at the fsize output, and thus one less than the number of samples that are to be read. This is used as the preload-value of the Event DCounter component, which counts down by one, each time that a new sample is read. The preload value needs to be one less than the number of samples that are to be read, because it counts down to zero, before ending the reading of samples, rather than 1.

In normal integration mode, the 2 most significant bits of the output count, are used as the address of the slave that is to be read, such that 32 16-bit samples are read from one slave at a time, starting with the 4th slave, and working down to the 1st slave. Note that this relies on the use of a zero-relative countdown.

```

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity frame_sizer is

Port (dsize : in std_logic_vector(15 downto 0);

dump : in std_logic;

fsize, fmax : out std_logic_vector(15 downto 0));

end frame_sizer;

architecture Behavioral of frame sizer is

-- Parameterize the total size of the FIFO in the Frame Buffer module.

constant buffer_size : std_logic_vector(15 downto 0) := "0100000000000000";

-- Create a wire for internal routing of the computed frame size.

signal frame_size : std_logic_vector(15 downto 0);

begin

-- Compute the number of 16-bit samples to be read from the slaves.

"000000010000000" when dump='0' else -- 64 integrated 32-bit samples.

"00000001000000" when dump- v else dsize when dsize < buffer_size else -- dump_lim_reg dump-mode samples buffer size; -- Limit to the size of the buffer.

-- Present the result at the fsize output.

fsize <= frame size:

-- Compute the preload value for a zero-relative down-counter of samples.

fmax <= frame size - 1:

end Behavioral;

```

Figure 3.14: The VHDL implementation of the Frame Sizer

In dump mode, the slave that is to be read, is not selected by the output count. Instead, MUX1 arranges that all of the dump-mode samples be loaded from the single slave that is specified by the dslave input.